## MULTIPLE CHOICE. Choose the one alternative that best completes the statement or answers the question.

| 1) The carry output of a ha                   | alf-adder circuit can be exp | oressed as              |

|-----------------------------------------------|------------------------------|-------------------------|

| $\Delta \setminus C \longrightarrow \Delta B$ | $B \cap C = A \cap B$        | $C)C \longrightarrow A$ |

- D) None of these

- 2) The expression A

B represents

- A) The carry output of a full-adder

- B) The summing output of a full-adder

- C) The summing output of a half-adder

- D) The carry output of a half-adder

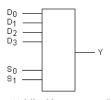

Figure 6-1

- 3) The symbol in Figure 6-1 represents a(n) B) PLD

- A) AND function

- - C) Half-adder

- D) Full-adder

- 4) Refer to the symbol in Figure 6–1. When A=0 and B=1,

- A)  $\Sigma = 1$ ,  $C_{out} = 0$

- B)  $\Sigma = 0$ ,  $C_{out} = 1$

- C)  $\Sigma = 0$ ,  $C_{out} = 0$

- D)  $\Sigma = 1$ ,  $C_{out} = 1$

- 5) What is the major difference between half-adders and full-adders?

- A) Full-adders can handle double digit numbers.

- B) Half-adders can only handle single digit numbers.

- C) Full-adders have a carry input capability.

- D) Nothing basically; full-adders are made up of two half-adders.

- 6) A BCD-to-decimal decoder has data input lines and data output lines. A) 7,9 B) 10,10 C) 4, 10

- D) 1,10

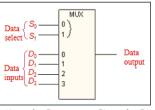

7) The circuit below is most likely a \_\_

- A) full-adder

- B) demultiplexer

- C) comparator

- D) multiplexer

8) The circuit below is most likely a \_\_\_\_

- A) demultiplexer

- B) multiplexer

- C) full-adder

C) HIGH

- D) comparator

D) LOW

11) \_

12)

- 9) A device that is used to switch one of several input lines to a single output line is called a A) multiplexer B) demultiplexer C) decoder D) comparator

- 10) If the data select lines of the MUX are  $S_1 S_0 = 11$ , the output will be

- A) equal to  $D_2$ B) equal to  $D_0$

- 11) What distinguishes the look-ahead-carry adder?

- A) It is easier to implement logically than a full-adder.

- B) It is slower than the ripple-carry adder. C) It is faster than a ripple-carry adder.

- D) It requires advance knowledge of the final answer.

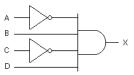

Figure 6-3

- 12) The output of the decoder in Figure 6-3 will be 1 only when

- A) A = 0, B = 1, C = 0, D = 1

- B) A = 1, B = 1, C = 1, D = 1

- C) A = 0, B = 0, C = 0, D = 0

- D) A = 1, B = 0, C = 1, D = 0

Answer Key Testname: TEST C5

1) A 2) C 3) C 4) A 5) C 6) C 7) D 8) A 9) A 10) A 11) C 12) A

3